2. Alat dan bahan[Kembali]

A. Alat dan Bahan (Modul De Lorenzo)

1. Jumper

B. Alat dan Bahan (Proteus)

1. IC 74LS112 (JK filp flop)

2. Power DC

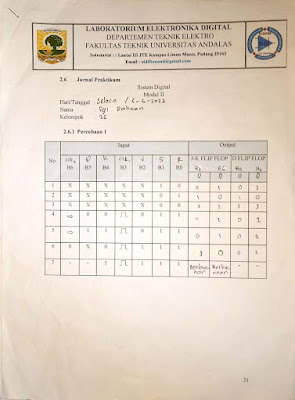

3. Rangkaian Simulasi[Kembali]

|

| Gambar 8 Rangkaian pada proteus |

4. Prinsip Kerja[Kembali]

↳ Pada percobaan input J dan K di hubungkan ke satu inputan sehingga Flip Flop ini disebut T Flip Flop

↳ Pada percobaan Modul 2 menggunakan IC 74LS112 yang merupakan jenis dari IC J-K Flip Flop. Pada percobaan , terdapat 4 kaki inputaan yaitu R (reset) dihubungkan ke B0, kaki S (set ) dihubungkan ke B1, kaki J-K dengan inputan sama dihubungkan ke VCC,kemudian untuk kaki clk dihubungkan ke B2. Untuk output sendiri yaitu untuk Q dihubungkan ke LED H7 dan Q' dihubungkan ke LED H6. Pada Rangkaian ini kaki R dan S bersifat aktif low ini berarti akan aktif jika berlogika 0 atau di proteus akan aktif ketika di hubungkan ke Ground.

Pada rangkaian Flip Flop yang akan di pengaruhi Output adalah inputan Set , Reset, T dan Clock dimana ketika harus memperhatikan kondisi Set dan Reset terlebih dahulu dimana jika Ketika Inputan Set aktif akan menjadikan output Q menyala atau berlogika 1 dan Q' berlogika 0 dan Input Reset aktif akan membuat Inputan Q menjadi 0 dan Q' menjadi 1 dan ketika Set dan Reset aktif maka output Q dan Q' akan berlogika 1.Ketika Kondsi Ser dan Reset tidak Aktif maka yang akan mempengarui Input adalah inputan dari T dengan ketentuan Clock harus dalam keadaan Aktif low atau berlogika 1(switch dari 0 dan 1).

- Apabila R=0, S=1 , T = Don"t care dan Clock= don't care, maka untuk output yang dihasilkan adalah Q=0 dan Q'=1. ini disebabkan Pin dari Reset aktif karena berlogika nol dan akan menyebabkan Ouput Q=0 dan Q'= 1

- Apabila R=1, S=0 ,T = Don"t care dan Clock= don't care, maka untuk output yang dihasilkan adalah Q=1 dan Q'=0. ini disebabkan Pin dari Set aktif karena berlogika nol dan akan menyebabkan Ouput Q=1 dan Q'= 1

- Apabila R=0, S=0 ,T = Don"t care dan Clock= don't care, maka untuk output yang dihasilkan adalah Q=1 dan Q'=1. ini disebabkan Pin dari Set dan Reset aktif karena berlogika nol dan akan menyebabkan Ouput Q=1 dan Q'= 1

- Apabila R=1, S=1, T = 1 dan Clock = aktif low (di switch dari 0 ke 1 secara terus menerus), maka untuk output yang dihasilkan bersifat toggle Q dan Q' aktif bergantian.,dimana berawal dari Q bernilai 1 (LED nyala) dan Q = 0 (lampu mati) selalu bergatian. hal ini dipengaruhi oleh clock yang aktif ketika berlogika 1 sehingga saat clock aktif maka nilai input J berlogika 1 aktif menyebabkan nilai output Q=0 dan Q'=1 dan terus bergantian selama clock aktif.

-> Analisa apa yang terjadi saat B2 dan Input J dan K dihubungkan ke Clock ,Gambarkan Timing Diagramnya!

Jawab :

Pada Input J dan K yang dihubungkan pada satu satu inputan kita hubungakan dengan Clock dengan kondisi R-S non aktif dan pin dr clock bersifat aktif low sehingga akan aktif ketika berlogika 0 sehingga Clock akan mempengaruhi nilai dari inputan J-K atau T yang mana akan membuat Inputan T berlogika 0 juga dan menyebabkan Q berlogika 0 dan Q' berlogika 1 hal ini sama prinsipnya dengan J-K flip flop.

7. Download[Kembali]

- HTML Klik disini

- Simulasi Proteus Klik disini

- Video Percobaan pada modul De Lorenzo Klik disini

- Video Percobaan pada Proteus Klik disini

- Datasheet IC 74LS112 klik disini

- Datasheet Switch klik disini

- Data sheet LED: Klik Disini

.jpeg)