2. Alat dan bahan[Kembali]

A. Alat dan Bahan (Modul De Lorenzo)

1. Jumper

B. Alat dan Bahan (Proteus)

1. IC 74LS112 (JK filp flop)

2. IC 7474 (D Flip Flop)

3. Power DC

3. Rangkaian Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

Flip flop merupakan rangkaian elektronika yang memiliki dua kondisi stabil dan dapat digunakan untuk menyimpan informasi.

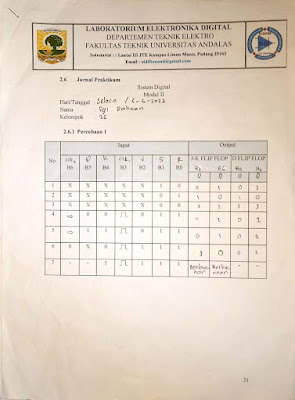

↠ Gambar rangkaian di atas merupakan gambar rangkaian J-K Flip Flop dan D Flip Flop dengan kondisi Awal B0=1, B1=1, B2=0, B3=1, B4= 0, B5=0, B6=1.

↠Pada gambar rangkaian di atas, terdapat J-K flip flop di bagian kana rangkian, Pada rangkaian percobaan 1 ini, digunakan jenis IC 74LS112 dan IC 7474 dimana pada J-K Flip Flop terdapat 5 buah pin inputan (J, K, Set , Reset dan Clock) pada percobaan terlihat bahwa untuk kaki R (reset) dihubungkan ke Swicth B0 dan Inputan R merupakan Aktif low (akan aktif jika berlogika 1). Untuk kaki S (set) dihubungkan ke Swich B1 dan bersifat aktif low, Untuk kaki J dihubungkan ke swicht B2 , Untuk CLK dihubungkan ke B3 dimana posisi clock disini adalah aktif low, dimana dia akan aktif jika bernilai 0. Selanjutnya, untuk Pin K dihubungkan ke Swicht B4. Pada rangkaian J-K Flip Flop yang akan di pengaruhi Output adalah inputan Set , Reset, J dan K dimana ketika harus memperhatikan kondisi Set dan Reset terlebih dahulu dimana jika Ketika Inputan Set aktif akan menjadikan output Q menyala atau berlogika 1 dan Q' berlogika 0 dan Input Reset aktif akan membuat Inputan Q menjadi 0 dan Q' menjadi 1 dan ketika Set dan Reset aktif maka output Q dan Q' akan berlogika 1.Ketika Kondsi Ser dan Reset tidak Aktif maka yang akan mempengarui Input adalah inputan dari J, K dengan ketentuan Clock harus dalam keadaan Aktif low atau berlogika 1.

⇉ Pada Rangkaian T Flip Flop, Maka output akan dipengaruhi oleh Kondisi sebagai berikut:

- Saat R=0, S=1, J=don't care, Clk=don't care, K=don't care,maka dihasilkan output Q=0 dan Q'=1.

- Saat R=1, S=0, J=don't care, Clk=don't care, K=don't care,maka dihasilkan output Q=1 dan Q'=0.

- Saat R=0, S=0, J=don't care, Clk=don't care, K=don't care,maka dihasilkan output Q=1 dan Q'=1.

- Saat R=1, S=1, J=1, Clk=aktif low (di switch dari 1 ke 0), K=0,maka dihasilkan output Q=1 dan Q'=0.

- Saat R=1, S=1, J=0, Clk=aktif low (di switch dari 1 ke 0), K=1,maka dihasilkan output Q=0 dan Q'=1.

- Saat R=1, S=1, J=1, Clk=aktif low (di switch dari 1 ke 0 secara trus menurus), K=1,maka dihasilkan output Q= berlawanan dan Q'= berlawanan.

↠Selanjutnya, adalah rangkaian D flip flop yang terletak pada bagian sebelah kiri. Untuk D flip flop terdapat 4 Inputan (D ,Clock , Set dan Reset), Dimana switch B5 dihubungkan ke kaki D.Kemudian switch B6 dihubungkan ke pin clock . Pada Rangkaian ini inputan Set besifat aktif low yang berarti akan aktif ketika diberi Inputan 0 atau kita hubungkan ke ground. dan jika Pin Set aktif maka mengakibatkan nilai dari outputnya akan dipengaruhi oleh oleh Set yang mana akan membuat nilai dari Output atau Q bernilai 1 dan Q' bernilai 0 dan pada percobaan nilai dari Reset juga bersifat aktif low akan aktif jika berlogika nol atau pada percobaan jika di hubungkan ke ground. Akan tetapi jika Set dan Reset off atau dihubungkan ke Vcc maka nilai dari output Q akan dipengaruhi oleh masukan D dan Clock. Yang mana inputan D di pengaruhi oleh nilai clock yang aktif. disini Inputan PIn Clock aktif high dimana akan aktif jika berlogika 1 atau saat kita mengubah switch dari 0 ke 1 sehingga onput D akan aktif. sehingga kalau kita simpulkan Output akan di pengaruhi oleh :

-> Input S ON, R OFF , D dan clock bersifat dont care maka membuat output Q = 1 dan Q= 0

-> Input S OFF, R ON , D dan clock bersifat dont care maka membuat output Q = 0 dan Q= 1

-> Input S ON, R ON , D dan clock bersifat dont care maka membuat output Q = 1 dan Q= 1

-> Input S OFF, R OFF , D berlogika 1 dan clock ON maka membuat output Q = 1 dan Q= 0

-> Input S OFF, R OFF , D berlogika 0 dan clock ON maka membuat output Q = 0 dan Q= 1

ket : S dan R ON berarti inputannya dihubungkan ke Ground

S dan R OFF berarti inputannya dihubungkan ke VCC (power)

5. Video Percobaan[Kembali]

1. Video Percobaan pada Modul De Lorenzo

Soal Analisa Percobaan 1:

1. Analisa yang terjadi saat Input B3 dan B2 di hubungkan ke Clock dan K berlogika 1 serta gambarkan Timing Diagramnya!

Jawab :

Saat Input B3 yang terhubung ke pin J diberi inputan CLock dan K berlogika 1 dimana pada pin Clock Bersifat Aktif Low yang akan aktif ketika jika diberi logika Nol atau kita Groundkan. jadi ketika Pin Clock Aktif maka Pin J juga Aktif sehingga Clok Aktif saat berlogika Nol maka Pin J juga berlogika Nol yang menyebabkan Output dari Q=0 dan Q'=1 .

Berikut Timing Diagramnya.

jawab:

Ketika B5 dan B6 di hubungkan ke Clock maka output dari D flip-flop akan sama dengan input D dimana akan menghasilkan output yang selalu bergantian aktif antara Q dan Q'.ini samahalnya dengan dasar teori dari D Flip Flop yang mana akan menghasilkan output sama dengan Inputan (Output Q= Input D)

Gambar Timing Diagram.

7. Download[Kembali]

- HTML Klik disini

- Simulasi Proteus Klik disini

- Video Percobaan pada Modul De Lorenzo Klik disini

- Video Percobaan Proteus Klik disini

- Datasheet IC 74LS112 (J-K Flip Flop) klik disini

- Datasheet IC 7474 (D Flip Flop) klik disini

- Datasheet Switch klik disini

- Data sheet LED: Klik Disini

0 komentar:

Posting Komentar